Topics

Introduction to Microprocessors and Organization of 8085

Instruction Set and Programming of 8085

Introdcution to Inted X-86 Family

Introduction to Microcontroller

Networking Technology

- Introduction to Networking

- Types of Networks

- Multiplexing

- Study of Transmission media

- Coaxial cable (Cable Media)

- Twisted pair cable

- Fiber Optic Cable

- Unbounded (Wireless) Media

- Access Methods

- Network Topologies

- Ethernet (Network Architectures)

- Token-Ring (Network Architectures)

- Internet protocols

- Introduction to connectivity devices

- ADD r (Add Register); ADD M (Add memory) & ADI data (Add immediate)

- ADC r (Add register with carry); ADC M (Add memory with Carry) & ACI data (Add Immediate with carry)

- SUB r (Subtract Register); SUB M (Subtract memory) & SUI data (Subtract immediate)

- SBB r (Subtract register with borrow); SBB M (Subtract Memory with borrow) & SBI data (Subtract immediate with borrow)

- INR r (Increment register) & INR M (Increment register)

- DCR r (Decrement Register) & DCR M (Decrement Memory)

- INX rp (Increment register pair) & DCX rp (Decrement register pair)

- DAD rp (Add register pair to H and L)

- DAA-DECIMAL ADJUST ACCUMULATOR

Arithmetic Group of Instructions

These instructions handle arithmetic operations like addition, subtraction, increment, and decrement. The 8085 microprocessor can perform 8-bit and 16-bit addition, 8-bit 2's complement subtraction, and can increment or decrement the 8-bit contents of a register or memory location, as well as the 16-bit contents of a register pair or stack pointer.

ADD r (Add Register); ADD M (Add memory) & ADI data (Add immediate)

ADD r: (A) <- (A) + (r),

The content of register r is added to the contents of the accumulator. The result is placed in accumulator. This is one-byte instruction. For example ADD B

Contents of B are added to contents of accumulator. The result is placed in accumulator. All Flags are affected. Addressing Mode: Register Addressing

ADD M: (A) <- (A) + ((H) (L)),

This is one byte instruction. The content of memory location whose address is in the H and L registers is added to the accumulator's contents. The result is placed in accumulator. All flags are affected. Addressing Mode: Register indirect.

ADI data (Add immediate): (A) <- (A) + (byte 2),

This 2-byte instruction adds the second byte's value to the accumulator and stores the result back in the accumulator. For example, ADI 05H adds 05 to the accumulator and stores the result there. Addressing Mode: Immediate Addressing

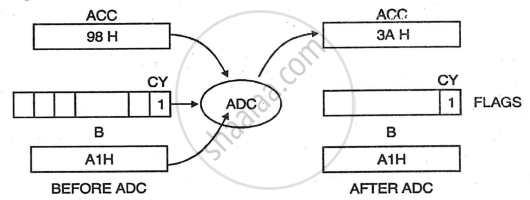

ADC r (Add register with carry); ADC M (Add memory with Carry) & ACI data (Add Immediate with carry)

In every instruction; all flags are affected during their execution

ADC r: (A) <- (A)+ (r) + (cy),

This is one byte instruction. The content of register r and the content of the carry bit are added to the content of the accumulator. The result is placed in accumulator. Addressing Mode: Register Addressing

For example: ADC B

Content of B along with carry bit are added to accumulator

ADC M: (A) <- (A)+ ((H) (L)) + (cy),

This is one byte instruction. The content of memory location whose address is contained in H and L registers and content of the CY flag are added to accumulator. The result is placed in accumulator. Addressing Mode: Register indirect.

ACI data: (A) <- (A)+ (byte 2) + (cy),

This is a 2 byte instruction. The content of second byte of the instruction and the content of cy flag are added to the contents of accumulator. The result is placed in accumulator. Addressing Mode: Immediate Addressing

SUB r (Subtract Register); SUB M (Subtract memory) & SUI data (Subtract immediate)

In every instruction; all the flags are affected

SUB r: (A) <- (A) - (r),

This is one byte instruction. The content of register r is subtracted from the content of accumulator. The result is placed in accumulator. Addressing Mode: Register Addressing

SUB M: (A) <- (A) - ((H) (L))

The content of memory location whose address is contained in the H and L registers is subtracted from the content of accumulator. The result is placed in accumulator. Addressing : Register Indirect.

SUI data: (A) <- (A) - (byte 2),

This 2-byte instruction subtracts the second byte's value from the accumulator and stores the result back in the accumulator. For example, SUI 05H subtracts 05H from the accumulator and stores the result there.

SBB r (Subtract register with borrow); SBB M (Subtract Memory with borrow) & SBI data (Subtract immediate with borrow)

SBB r: (A) <- (A) - (r) - (cy),

The contents of register r and carry bit are subtracted from content of accumulator. The result is placed in accumulator. This is one-byte instruction. Addressing Mode: Register Addressing

SBB M: (A) <- (A) - [(H) (L)] - (cy),

This instruction subtracts the content of the memory location pointed to by the HL register and the carry bit from the accumulator, then stores the result back in the accumulator. This is one byte instruction. Addressing Mode: Register indirect Addressing.

SBI data: (A) <- (A) - (byte 2) - (cy),

The content of the second byte of the instruction and the contents of cy flag are both subtracted from the accumulator. The result is placed in accumulator. This is a two byte instruction. Addressing Mode: Immediate Addressing.

INR r (Increment register) & INR M (Increment register)

INR r: (r) <- (r) + 1,

The contents of register r are incremented by one. This is one byte instruction. All flags except cy flag are affected. r can be A, B, C, D, E, H, and L. Addressing Mode: Register Addressing Mode

INR M: [(H) (L)] <- [(H) (L)] + 1,

Same as the above instruction; the only difference is the content which is to be incremented is in a memory location pointed by HL Pair. All flags except carry flag are affected. Addressing Mode: Register Indirect Mode.

DCR r (Decrement Register) & DCR M (Decrement Memory)

DCR r: (r) <- (r) - 1 ,

The content of register r is decremented by one. All flags except cy are affected.

DCR M: [(H) (L)] <- [(H) (L)] - 1

The content of memory location whose address is contained in the H and L registers is decremented by one. All condition flags except cy are affected.

INX rp (Increment register pair) & DCX rp (Decrement register pair)

INX rp: [(rh) (rl)] <- [(rh) (rl)] + 1,

The content of register pair rp is incremented by one. No flags are affected. Addressing Mode: Register Addressing

DCX rp: [(rh) (rl)] <- [(rh) (rl)] - 1,

The content of register pair rp is decreased by one. No flags are affected. Addressing Mode: Register Addressing

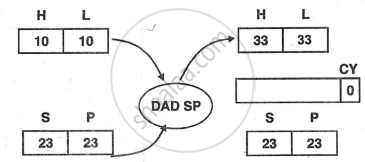

DAD rp (Add register pair to H and L)

(H) (L) <- (H) (L) + (rh) (rl),

The content of register pair rp is added to the content of the register pair H and L. The result is placed in register H and L. Only Cy flag is affected.

DAA-DECIMAL ADJUST ACCUMULATOR

This special arithmetic instruction adjusts the binary contents of the accumulator into two 4-bit BCD digits. It is the only instruction that uses the Auxiliary Carry (AC) flag for adjustment, which the CPU handles internally. All flags are updated based on the result. This instruction must follow an addition operation for two BCD numbers, adjusting their sum to BCD format. It does not convert binary numbers to BCD and cannot adjust results after subtraction.

The adjustment procedure is:

- Perform BCD addition (previous instruction).

- If the lower nibble of the accumulator is greater than 9 or the AC flag is set, add 06 to the lower nibble.

- If the upper nibble of the accumulator is greater than 9 or the C flag is set, add 06 to the upper nibble.

- If both nibbles are greater than 9 or the AC and C flags are set, add 66 to the accumulator.

Example: 36H= (0011 0110)2

+29H= (0010 1001)2

----------------------------

5FH= (0101 1111)2

+ 6H= (0000 0110)2

-----------------------------

65H (0110 0101)2