Topics

Introduction to Microprocessors and Organization of 8085

Instruction Set and Programming of 8085

Introdcution to Inted X-86 Family

Introduction to Microcontroller

Networking Technology

- Introduction to Networking

- Types of Networks

- Multiplexing

- Study of Transmission media

- Coaxial cable (Cable Media)

- Twisted pair cable

- Fiber Optic Cable

- Unbounded (Wireless) Media

- Access Methods

- Network Topologies

- Ethernet (Network Architectures)

- Token-Ring (Network Architectures)

- Internet protocols

- Introduction to connectivity devices

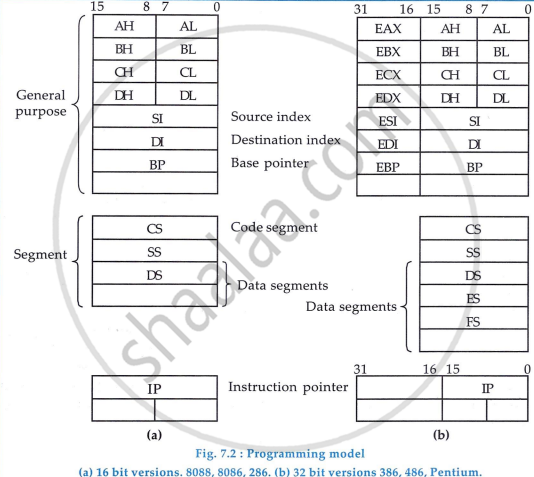

- Programming Model Diagram

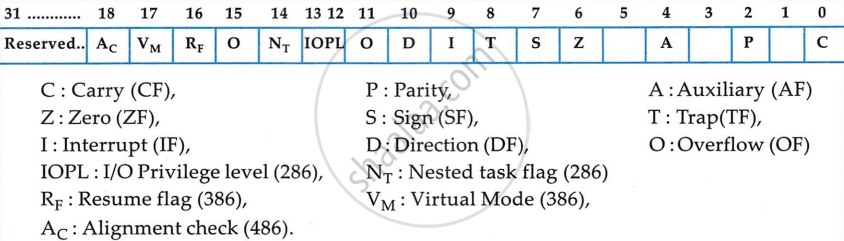

- Flag Register in X 86 Family

- Additional Features

Programming model for X-86 family of Advanced Microprocessor

The 8088 and 8086 processors define the base programming model for the X86 family. Newer X86 processors, like the 386 and 486, offer greater computing power with faster speeds, 32-bit registers, and advanced addressing. The programming model consists of three register groups: eight general-purpose registers (AX, BX, CX, DX, SI, DI, BP, SP), which become 32-bit (EAX, EBX, etc.) in newer processors; segment registers (CS, SS, DS, ES, FS, GS) for managing memory operations; and the instruction pointer (IP) and flag register, which are either 16-bit or 32-bit, depending on the processor. These registers handle data storage, memory operations, and instruction execution.

Programming Model Diagram

Flag Register in X 86 Family

The first 5 bits are identical to 8085 flag. The bits 6 - 11 were introduced with 8088/8086. The bits 12- 14 were introduced with 286. 16th and 17th bits were introduced with 386 and 18th was introduced with 486

Additional Features

X86 processors enhance speed through instruction prefetching and data caching. They cache instructions in an internal memory or prefetch queue, making them instantly available for processing, thus reducing fetch cycle delays. Additionally, frequently used data is stored in an on-chip cache, minimizing the need for external memory access and further accelerating processing time.