Topics

Introduction to Microprocessors and Organization of 8085

Instruction Set and Programming of 8085

Introdcution to Inted X-86 Family

Introduction to Microcontroller

Networking Technology

- Introduction to Networking

- Types of Networks

- Multiplexing

- Study of Transmission media

- Coaxial cable (Cable Media)

- Twisted pair cable

- Fiber Optic Cable

- Unbounded (Wireless) Media

- Access Methods

- Network Topologies

- Ethernet (Network Architectures)

- Token-Ring (Network Architectures)

- Internet protocols

- Introduction to connectivity devices

- ANA r (AND register); ANA M (AND memory) & ANI data (AND immediate)

- XRA r (Exclusive OR Register); XRA M (Exclusive OR memory) & XRI data (Exclusive OR immediate)

- ORA r (OR register); ORA M (OR memory) & ORI data (OR immediate)

- CMP r (Compare Register) & CMP M (Compare Memory)

- RLC (Rotate Left) & RRC (Rotate Right)

- RAL (Rotate left through carry) & RAR (Rotate Right through carry)

- CMA (Complement accumulator); CMC (Complement carry) & STC (Set carry)

Logical Instructions

ANA r (AND register); ANA M (AND memory) & ANI data (AND immediate)

ANA r: (A) <- (A) /\ (r),

The contents of register r is logically AND ed with the content of accumulator. The result is placed in accumulator. The cy flag is cleared and AC is set. This is one byte instruction.

Addressing Mode: Register Addressing.

ANA M: (A) <- (A) /\ ((H) (L)),

Same as previous instruction; the difference is the content to be AND ed is present in a memory location pointed by HL Pair. The CY flag is cleared and AC is set. This is one byte instruction. Addressing Mode: Register indirect.

ANI data: (A) <- (A) /\ (byte 2),

Two byte instruction. Here the content to be AND ed is provided in the second byte of instruction. The CY flag is cleared and AC is set. Addressing Mode: Immediate Addressing.

XRA r (Exclusive OR Register); XRA M (Exclusive OR memory) & XRI data (Exclusive OR immediate)

XRA r: (A) <- (A) ⊕ (r),

The content of register r is exclusive OR'ed with the content of accumulator. The result is placed in accumulator. The CY and AC flags are cleared. This is one byte instruction. Addressing Mode: Register Addressing.

XRA M: (A) <- (A) ⊕ [(H) (L)],

Everything same as the previous instruction the only difference lies in the content which is to exclusive OR’ed being present in a memory location pointed by HL Pair. Addressing Mode: Register Indirect.

XRI data: (A) <- (A) ⊕ (byte 2),

This is a two byte instruction. The content to be exclusive OR’ed is present is the second byte instruction. The CY and AC flags are cleared. The result is place in accumulator. . Addressing Mode: Immediate Addressing.

ORA r (OR register); ORA M (OR memory) & ORI data (OR immediate)

ORA r: (A) <- (A) V r,

The content of the register r is inclusive OR' ed with the content of the accumulator. The result is placed in the accumulator. The CY and AC flags are cleared. Addressing Mode: Register

ORA M: (A) <- (A) v ((H) (L)),

Everything same as the previous instruction the only difference lies in the content which is to OR’ed being present in a memory location pointed by HL Pair. Addressing Mode: Register Indirect.

ORI data: (A) <- (A) v (byte 2),

This is a two byte instruction. The content to be OR’ed is present is the second byte instruction. The CY and AC flags are cleared. The result is place in accumulator. Addressing Mode: Immediate Addressing.

CMP r (Compare Register) & CMP M (Compare Memory)

CMP r: (A) - (r),

The content of register r is subtracted from the accumulator without changing the accumulator. Condition flags are updated: the Z flag is set to 1 if (A) equals (r), the CY flag is set to 1 if (A) is less than (r) and none of CY or Zero Flag is set when (A)>(r). , Addressing : Register Addressing.

CMP M: (A) - ((H) (L))

Everything is same as in the previous instruction just the content to be compared is in a memory location pointed by HL Pair. Addressing Mode: Register Indirect.

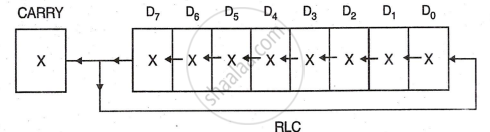

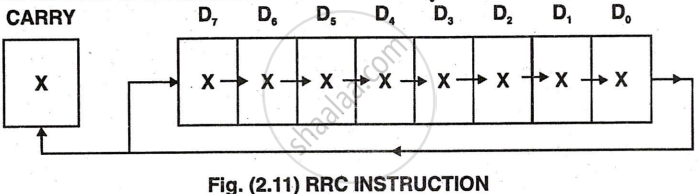

RLC (Rotate Left) & RRC (Rotate Right)

Note: RLC: (An+ 1) <- (An); (A0) <- (A7)

(CY) <- (A7)

The content of the accumulator is rotated left one position. The low order bit and the CY flag are both set to the value shifted out of the high order bit position. Only the CY flag is affected. This is one byte instruction.

RRC: (An) <- (An +1) ; (A7) <- (A0)

(CY) <- (A0).

The content of accumulator is rotated right one position. The higher order bit and the CY flag are both set to the value shifted out of the low order bit position. Only the CY flag is affected. This is one byte instruction.

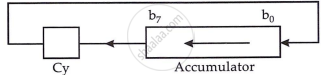

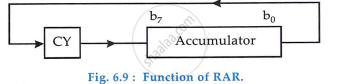

RAL (Rotate left through carry) & RAR (Rotate Right through carry)

RAL: (An +1) <- (An); (CY) <-(A7)

(A0) <- (CY)

The content of accumulator is rotated left one position through the CY flag. The low-order bit is set equal to the CY flag and the CY flag is set to the value of shifted out of the high order bit. Only the cy flag is affected

RAR: (An) <- (An+ 1) ; ( cy) <- (A0)

(A7) <- (cy)

The content of the accumulator is rotated right on position through the CY flag. The high order bit is set to the CY flag and the CY flag is set to the value shifted out of the low order bit. Only the cy flag is affected.

CMA (Complement accumulator); CMC (Complement carry) & STC (Set carry)

CMA: (A) <- (A bar)

The contents of accumulator are complemented (Zero bits become 1, one bits becomes 0). No flags are affected . This is one byte instruction.

CMC: (cy) <- (cy bar)

The carry flag is complemented. No other flags are affected

STC: (cy) <- 1.

Carry flag is set to 1. No other flags are affected.